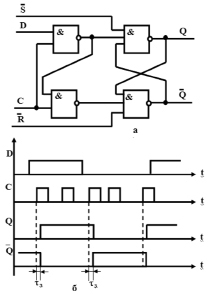

D-триггер (от англ. delay) отличается от синхронного RS-триггера тем, что вместо двух информационных входов R и S у него имеется только один информационный вход D (рис. 1, а). Часто его называют триггером задержки. Предположим, что первоначально триггер находится в нулевом состоянии, т.е. Q = 0. Если на вход D подать логическую «1», а на вход С подать тактирующий импульс, то на выходе Q установится логическая «1», т.е. триггер примет единичное состояние (Q = 1). Если на вход D подать логический «0», а на вход С – следующий импульс, то триггер перейдет в нулевое состояние (Q = 0). Поступление новых синхроимпульсов на вход С без смены сигнала на информационном входе, не может изменить состояние триггера (рис. 1, б).

Каждый раз смена состояния триггера совершается только по переднему фронту тактирующего импульса на входе С с небольшой задержкой tз по переднему и заднему фронту.

Асинхронные  и

и  входы имеют приоритет перед информационным, поскольку элемент памяти в этом случае управляется Лог.

входы имеют приоритет перед информационным, поскольку элемент памяти в этом случае управляется Лог.

Рис. 1. Комбинированный RS – D триггер (а) и его временные диаграммы (б)

«0» (Q = 1) и уже его ничто не может изменить (табл. 1). Чтобы иметь возможность записать информацию на входе D, следует подать на входы  и

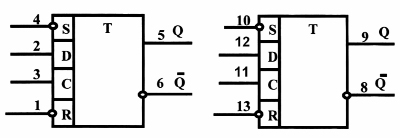

и  логическую «1». Условно-графическое изображение D-триггера представлено на рис. 2. На возможность управления триггером только низким потенциалом по входам S и R указывает знак инверсности.

логическую «1». Условно-графическое изображение D-триггера представлено на рис. 2. На возможность управления триггером только низким потенциалом по входам S и R указывает знак инверсности.

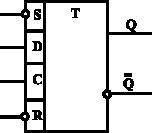

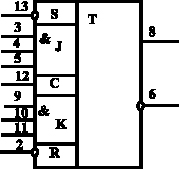

Если информационный вход D триггера соединить с его инверсным выходом  , то у триггера остается только один вход С (без учета R и S). При поступлении серии импульсов на вход С, триггер меняет свое состояние каждый раз по переднему фронту этих сигналов и, поскольку лог. «1» на выходе Q появляется в два раза реже, чем импульсы на входе С, то такой триггер осуществляет деление частоты входных сигналов на два. В этом случае такой триггер называют счетным или Т-триггером. Запрещенным состоянием для D-триггера считается одновременное присутствие на входах R = S = 0, в результате чего на обоих выходах возникает логическая «1» (табл. 1). В настоящей работе изучается D-триггер, построенный на ИМС типа К155ТМ2. Данная микросхема имеет в своем составе два независимых D-триггера, представленные на рис. 3.

, то у триггера остается только один вход С (без учета R и S). При поступлении серии импульсов на вход С, триггер меняет свое состояние каждый раз по переднему фронту этих сигналов и, поскольку лог. «1» на выходе Q появляется в два раза реже, чем импульсы на входе С, то такой триггер осуществляет деление частоты входных сигналов на два. В этом случае такой триггер называют счетным или Т-триггером. Запрещенным состоянием для D-триггера считается одновременное присутствие на входах R = S = 0, в результате чего на обоих выходах возникает логическая «1» (табл. 1). В настоящей работе изучается D-триггер, построенный на ИМС типа К155ТМ2. Данная микросхема имеет в своем составе два независимых D-триггера, представленные на рис. 3.

Рис. 3. Расположение выводов ИМС К155ТМ2

Таблица 1

Таблица истинности D-триггера

|

ВХОДЫ |

ВЫХОДЫ |

||||

|

S |

R |

D |

C |

Q |

Q |

|

0 |

1 |

* |

* |

1 |

0 |

|

1 |

0 |

* |

* |

0 |

1 |

|

1 1 1 |

1 1 1 |

1 0 1 |

|

1 0 1 |

0 1 0 |

|

0 |

0 |

* |

* |

1 |

1 |

Примечание. Символы  в табл. 1 означают кратковременный положительный перепад.

в табл. 1 означают кратковременный положительный перепад.

Рис. 2. Графическое изображение RS – D триггера

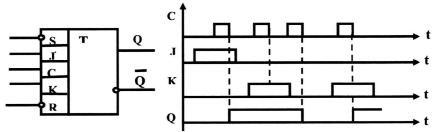

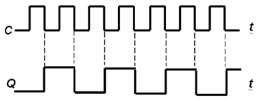

Наиболее универсальным среди тактируемых является JK-триггер (от англ. Jump и Keep), отличающийся от рассмотренных тем, что появление на обоих информационных входах (J и K) логических нулей приводит к изменению состояния триггера. Такая комбинация сигналов для JK-триггера не является запрещенной. Схемная реализация JK-триггера достаточно сложная. Однако, применяя ИМС, нам необязательно обращаться к внутреннему их устройству и обычно достаточно бывает знакомства с их параметрами и функциями, определяемыми условным изображением (рис. 4).

а) б)

Рис. 4. Универсальный JK – триггер (а) и его временные диаграммы (б). Примечание: 1)  символ означает отрицательный перепад напряжения от высокого уровня к низкому. 2) Занесение информации в JK-триггер происходит по отрицательному перепаду напряжения на входе С

символ означает отрицательный перепад напряжения от высокого уровня к низкому. 2) Занесение информации в JK-триггер происходит по отрицательному перепаду напряжения на входе С

Таблица 2

Таблица истинности JK-триггера

|

ВХОДЫ |

ВЫХОДЫ |

|||||

|

S |

R |

J |

K |

C |

Q |

Q |

|

0 0 1 1 0/1 1 1 1 1 |

0 1 0 1 1 1 1 1 1 |

* * * 0 0 0 1 1 1 |

* * * 0 0 1 0 1 1 |

|

1 1 0 0 1/1 0 1 0 1 |

1 0 1 1 0/0 1 0 1 0 |

JK-триггер не имеет запрещенных входных комбинаций. Но в реальных микро-схемах используется комбинация RS-триггера с JK-триггером. Установка такого триггера по RS – и J, С, K – входам производится независимо. При одновременном поступлении сигналов на R-, либо на S-вход и на J, С, K – входы, первые имеют приоритет над вторыми. Реальный JK-триггер, построенный на ИМС К155ТВ1, имеет по три информационных J- и по три К-входов, сгруппированных в элементы «И». Логика 3И на входе означает, что значение сигнала J = 1 будет только в том случае, если J1 = J2 = J3 = 1. Аналогично значения сигнала К = 1 будет только в том случае, если К1 = К2 = К3 = 1. Как правило, из входов {J} используется только один, а остальные два входа остаются неподклю-ченными, что равносильно подаче лог. «1» на них. То же самое справедливо и для входов (К) (рис. 5).

Рис. 5. Универсальный JК-триггер на ИМС К155ТВ1

JК-триггер тоже может работать как триггер со счетным входом. Если на входы J- и К-подать лог «1», то в соответствии с табл. 2 истинности, по отрицательному перепаду входных импульсов JК-триггер будет переходить в состояние, инверсное предыдущему (рис. 6).

Из этой диаграммы видно, что триггер со счетным входом делит на два частоту следования входных синхроимпульсов.

Рис. 6. Временные диаграммы JK-триггера в счетном режиме

Порядок выполнения работы

Задание 1

Изучение D- триггера в статическом режиме.

1.1. Ориентируясь на графическое изображение схемы D–триггера на ИМС К155ТМ2 (рис. 3), начертить схему электрическую принципиальную, предназначенную для исследования комбинированного RS-D-триггера в статическом режиме. Схема должна учитывать:

а) задание информации на S, R и D – входы от тумблеров SA1-SA3;

б) подачу синхроимпульсов на вход С от одной из кнопок SB1-SB4 (контакты К1-К4) блока формирователей сигналов без дребезга;

в) подключение единичного выхода триггера к контакту HL-A1 блока индикации 1;

г) подключение инверсного выхода триггера к контакту HL-B1 блока индикации 1.

1.2. Составить и заполнить таблицу соединений.

1.3. Произвести монтаж схемы по таблице.

1.4. После проверки правильности соединений включить блок питания стенда.

1.5. Составить и заполнить таблицу истинности RS- и D- триггера в виде:

|

ВХОДЫ |

ВЫХОДЫ |

||||

|

S |

R |

D |

C |

Q |

|

Необходимо помнить, что входы S- и R- имеют приоритет перед входами D- и C-.

1.6. Найти неисправность, внесенную в схему преподавателем.

1.7. Выключить блок питания, демонтировать схему.

Задание 2

Изучение JK – триггера в статическом режиме.

2.1. Начертить схему, предназначенную для исследования комбинированного RS – и JK- триггера на ИМСК155ТВ1.

Схема должна учитывать:

а) задание информации на входы S, R и J, K от тумблеров SA1-SA4;

б) подачу синхроимпульса от одной из кнопок SB1-SB4 (контакты  -

- ) блока формирователей сигналов без дребезга;

) блока формирователей сигналов без дребезга;

в) подключение единичного (прямого) выхода Q к контакту HL-А1 блока индикации 1;

г) подключение нулевого (инверсного) выхода Q триггера к контакту HL-B1 блока индикации 1.

2.2. Написать таблицу соединений.

2.3. Смонтировать на стенде схему.

2.4. После проверки правильности соединений преподавателем включить блок питания стенда.

2.5. Составить и заполнить таблицу истинности для исследования комбинированного RS- и JK-триггера:

|

ВХОДЫ |

ВЫХОДЫ |

|||||

|

S |

R |

J |

K |

C |

Q |

|

Необходимо твердо помнить, что входы S и R имеют приоритет перед другими.

2.6. Найти неисправность, внесенную в схему преподавателем.

2.7. Выключить блок питания и демонтировать схему.

Задание 3

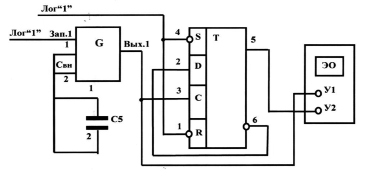

Исследование схемы комбинированного RS- и D-триггера в счетном режиме.

3.1. Смонтировать на стенде схему исследования D-триггера в счетном режиме (рис. 7).

3.2. После проверки правильности соединений, включить питание осциллографа и стенда.

3.3. Получить на экране осциллографа устойчивые изображения сигналов.

3.4. Убедиться в том, что триггер со счетным входом делить частоту следования входных сигналов на два, переключаясь по положительному перепаду;

3.5. Зарисовать в масштабе осциллограммы и определить параметры входных и выходных сигналов.

3.6. Определить быстродействие триггера путем измерения времени задержки выходного сигнала относительно входного.

3.7. Выключить питание приборов и демонтировать схему, сохранив схему генератора без нарушений.

Задание 4

Исследование комбинированного RS-JK-триггера в счетном режиме.

4.1. Начертить схему для исследования универсального RS- JK-триггера на ИМС К155ТВ1 в счетном режиме, аналогичную рис. 7.

Рис. 7. Работа D-триггера в счетном режиме

4.2. Схема должна учитывать:

а) подачу потенциала лог. «1» от контактов блока переключателей SA на входы S, R, J, K;

б) подачу синхроимпульсов от генератора на вход «С» и на вход У1 осциллографа;

в) подключение прямого выхода триггера на вход У2 осциллографа;

4.3. После проверки правильности соединений, включить питание осциллографа и стенда.

4.4. Получить на экране осциллографа устойчивые изображения входных и выходных сигналов.

4.5. Убедиться в том, что триггер делит частоту входных сигналов на два, переключаясь каждый раз по отрицательному перепаду.

4.6. Зарисовать в масштабе осциллограммы входных и выходных сигналов и определить их параметры.

4.7. Определить быстродействие триггера путем измерения задержки выходного сигнала относительно входного.

4.8. Выключить питание приборов и демонтировать схему.

4.9. Привести рабочее место в порядок и закончить работу.

Задание на дом

1. Изучить особенности принципа действия комбинированных RS- D и JK-триггеров.

2. Освоить принцип использования комбинированных триггеров в счетном режиме.

3. Освоить принцип последовательного деления частоты сигналов на 2; на 4 с помощью D- и JK-триггеров.

4. Освоить проверку работы триггеров в статическом и динамическом режимах.

5. Подготовить ответы на контрольные вопросы.

Контрольные вопросы

1. Проследите прохождение сигналов по структурной схеме D-триггера.

2. В каком случае комбинированный RS- и D-триггер переходит в счетный режим?

3. Как составляется таблица истинности D-триггера?

4. Как создаются положительные и отрицательные перепады напряжения для управления триггерами?

5. За счет чего возникает положительный потенциал на других входах JK-триггера при наличии его на одном из информационных (J или K)?

6. Особенности работы JK- триггера в счетном режиме?