Scientific journal

International Journal of Applied and fundamental research

ISSN 1996-3955

ИФ РИНЦ = 0,556

LOGIC ELEMENTS ON THE INTEGRATED CIRCUIT

Цель: Ознакомление с принципом построения логических элементов на интегральных микросхемах (ИМС) и методами исследования их в статике и динамике.

Логическими элементами называются устройства для преобразования числовой (дискретной) информации взаимообусловленности истинных и ложных суждений или высказываний. Простые суждения представляются элементарными функциями, состоящими из двух аргументов, которые могут быть обозначены различными математическими символами. Из элементарных логических функций могут быть составлены сложные логические функции. Число элементарных функций и их комбинаций определяется формулой  , где n = 0,1,2,…. Так, при n = 0 число элементарных функций составляет

, где n = 0,1,2,…. Так, при n = 0 число элементарных функций составляет  = 21 = 2; т.е. F1 = 1 и F2 = 0. При n = 1 множество элементарных функций состоит из 22 = 4 комбинаций (00, 01, 10, 11) и т.д.

= 21 = 2; т.е. F1 = 1 и F2 = 0. При n = 1 множество элементарных функций состоит из 22 = 4 комбинаций (00, 01, 10, 11) и т.д.

Двузначные суждения легко реализуются двухпозиционными элементами с двумя устойчивыми состояниями, такими, как логические элементы. И, ИЛИ, НЕ и их комбинациями. Исполнение этих элементов на диодной и диодно-транзисторной логике (ДТЛ) показало, что они имеют большую задержку выходного сигнала относительно входного.

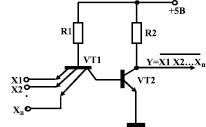

В настоящей работе нам надлежит исследовать транзисторно-транзисторную логику (ТТЛ), представленную интегральными схемами серии К155. Элементы такой логики имеют в десятки раз большее быстродействие и, соответственно, меньшую задержку, чем элементы ДТЛ. В ТТЛ – схемах базовым элементом является схема И-НЕ (рис. 1).

Рис. 1. Упрощенная схема элемента И-НЕ

С помощью этой схемы можно реализовать любую логическую функцию. Входным элементом является многоэмиттерный транзистор VT1, которого можно представить как схему И на диодах с нагрузкой R1 в цепи базы, как это было сделано в предыдущей работе. При поступлении на все входы сигналов высокого уровня, т.е. логической «1», на базе транзистора VT1 будет также высокий потенциал. Такой потенциал появится и на базе VT2. Тогда транзистор VT2 войдет в режим насыщения и на его коллекторе появится потенциал, соответствующий логическому «0». При поступлении на входы хотя бы одного лог. «0», на базе VT2 также будет низкий потен-циал. Тогда VT2 закрывается и транзистор переходит в режим отсечки. На коллекторе VT2 возникнет высокий потенциал. Т.о., если на входе схемы появится хотя бы один лог «0», то на выходе получим лог. «1». Поэтому данная схема реализует логику И-НЕ на n – входов. На практике обычно число входов этих элементов не превышает трех-четырех.

В процессе исследования логических элементов мы должны убедиться в том, что исследуемые схемы реализуют именно ту логическую функцию, которая указана на графическом его изображении. При этом значения аргументов задаются тумблерами, значение логической функции можно определить вольтметром как в предыдущей работе. Но удобнее это проводить с помощью элементов индикации, т.е. светоизлучающих диодов.

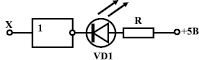

Светодиод к исследуемой схеме подключается через другой логический элемент типа НЕ (рис. 2, а). Диод будет светиться в том случае, если через него потечет достаточный ток. Последнее возможно при Х = 1. Если Х = 0, то на выходе элемента НЕ появится высокий потенциал и через диод тока не будет. Свечение диода условно принимается за лог. 1, а отсутствие свечения – за лог.0. С помощью световой индикации можно исследовать логические элементы в статике. Упрощенное изображение этой схемы показано на рис. 2, б.

а) б)

Рис. 2. Схема соединения светодиода (а) и его условно-графическое изображение (б)

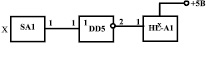

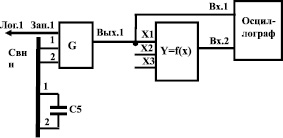

Для изучения работы логических элементов в динамике можно использовать схему, изображенную на рис. 3. Под Y = f(x) здесь подразумевается любой логический элемент, количество входов Xi которого определяется его типом. На вход Х1 подаются импульсные сигналы от генератора G, а значения остальных аргументов Х2…. Хn задаются с помощью тумблеров SA1-SA10. Входной сигнал Х1 изучается через первый, а выходной сигнал – через второй канал осциллографа. По осциллографу, измеряя запаздывание выходного сигнала относительно входного, можно определить быстродействие схемы.

Порядок выполнения работы

Задание 1

Статический режим работы логических элементов.

1.1. Исследовать в статике работу логического элемента НЕ на интегральной схеме DD5 типа К155ЛН1 (рис. 4). Результаты исследования выразить в виде таблицы истинности.

Рис. 4. Схема проверки элемента НЕ в статике

Примечание: ИМС типа К155ЛН1 включает в себе шесть элементов НЕ. Поэтому можно ограничиться проверкой только одного элемента. То же самое относится и к другим ИМС этой серии (см. Приложение 8).

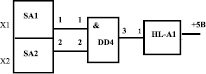

1.2. Исследовать в статике работу логического элемента И на ИМС DD4 типа К155ЛИ1 (рис. 5). Результаты исследования свести в таблицу истинности.

Рис. 5. Схема проверки элемента И в статике

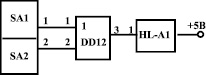

1.3. Исследовать в статике работу логического элемента ИЛИ на ИМС DD12 типа К155ЛЛ1 (рис. 6). Результаты исследования отразить ввиде таблицы истинности.

Рис. 6. Схема проверки элемента ИЛИ в статике

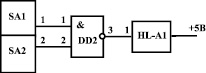

1.4. Исследовать в статике работу базового логического элемента 2И-НЕ на ИМС DD2 типа К155ЛА3 (рис. 7). Результаты исследования отразить в виде таблицы истинности.

Рис. 7. Схема проверки элемента И-НЕ в статике

Задание 2

Динамический режим работы логических элементов.

2.1. Исследовать в динамике работу логического элемента НЕ на ИМС DD5 типа К155ЛН1. Результаты исследований выдать в виде осциллограмм и данных измерений времени задержки по фронту tзф. Для изучения динамического режима используется схема на рис. 3.

Рис. 3. Схема проверки логических элементов в динамике

2.2. Исследовать в динамике работу логического элемента И на ИМС DD4 типа К155ЛИ1. Отчетность по заданию такая же, как в п. 1.1.

2.3. Исследовать в динамике работу базового логического элемента 2И-НЕ на ИМС DD2 типа К155ЛА3 с той же отчетностью.

Задание 3

Начертить и смонтировать на базе элемента 2И-НЕ на ИМС К155ЛА3 схему, реализующую функцию следующего вида: Y = X1˄X2.

Подсказка: Y = X1˄X2 = X1˄X2.

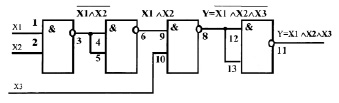

3.2. Начертить и смонтировать на базе элемента 2И-НЕ на ИМС К155ЛА3 схему, реализующую функцию следующего вида: Y = X1˄X2˄X3.

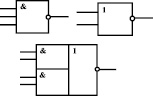

3.3. Такая схема может быть построена по образцу рис. 8.

3.4. Составить таблицу истинности схемы и экспериментально убедиться в справедливости выполняемой операции. Закончить работу, демонтировать схему и привести рабочее место в порядок.

Рис. 8. Схема реализации логической операции

Задание на дом

1. Подготовить отчет по теме.

2. Изучить логику работы логических элементов.

3. Освоить принципы построения простых логических элементов на транзисторах.

4. Освоить методы проверки логических элементов в статике и динамике.

5. Изучить принцип действия светоизлучающих диодов и возможность использования их для проверки состояния логических элементов.

6. Изучить и запомнить принцип маркировки ИМС (см. Приложение 3).

7. Подготовить ответы на контрольные вопросы.

Контрольные вопросы

1. Какую логическую функцию реализуют следующие схемы:

2. Какими способами можно получить элемент НЕ из базового логического элемента 2И-НЕ

3. Устройство элемента 2И-НЕ

4. Как проявляется ключевой режим транзистора в работе логических элементов?

5. Почему нужно знать время задержки входного сигнала при прохождении через логический элемент?

6. Какие преимущества имеет ТТЛ – логика перед ДТЛ-схемой?

7. Запомните следующие тождества:

А + А = А;  ; А + 0 = А; А + 1 = 1;

; А + 0 = А; А + 1 = 1;

А ˄ А=А;  ; А ˄ 0 = 0;

; А ˄ 0 = 0;

;

;

8. Составьте схемы, реализующие следующие функции:

У1 = (Х1VХ2)×Х3; У2 = (Х1VХ2) Х3;

Библиографическая ссылка

Мукашев К.М., Шадинова К.С., Жусипбекова Ш.Е., Жакипова Ш.А., Маметжанова Н.Х., Туймебаева А.Е., Жыланбаева Б.К., Баракова А.Ш. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ // Международный журнал прикладных и фундаментальных исследований. 2016. № 5-3. С. 382-385;URL: https://applied-research.ru/en/article/view?id=9259 (дата обращения: 13.05.2026).